flipflop - Signal in and out of flip according to IEEE symbols - Electrical Engineering Stack Exchange

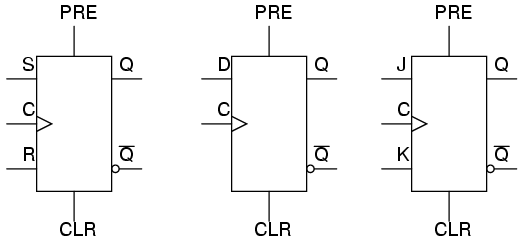

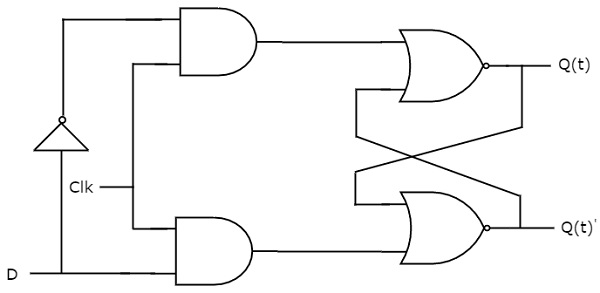

The conventional D-type flip-flop (DFF) symbol (a) and an example of... | Download Scientific Diagram

Q. 5.19: A sequential circuit has three flip-flops A, B, C; one input x_in; and one output y_out. - YouTube

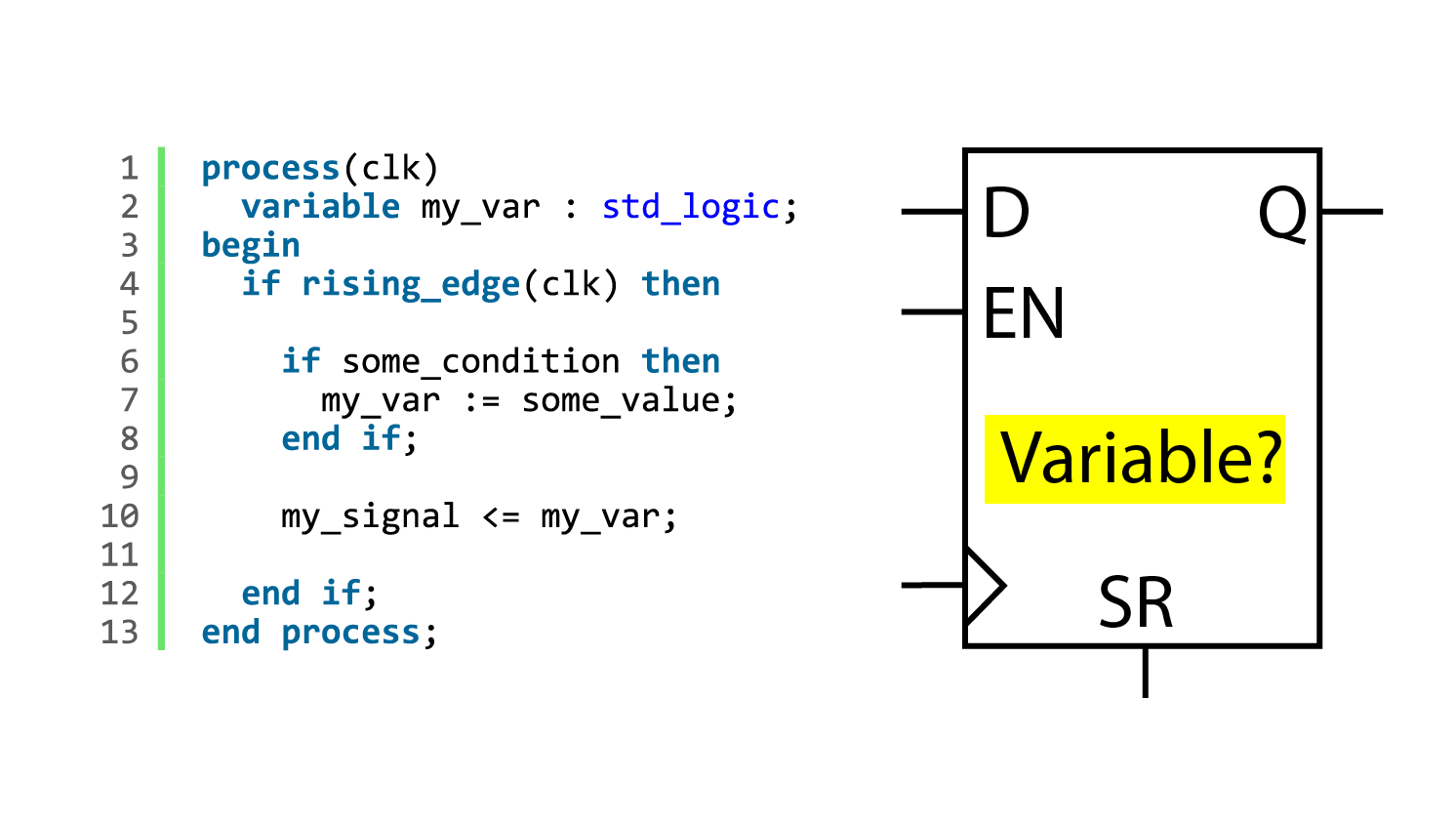

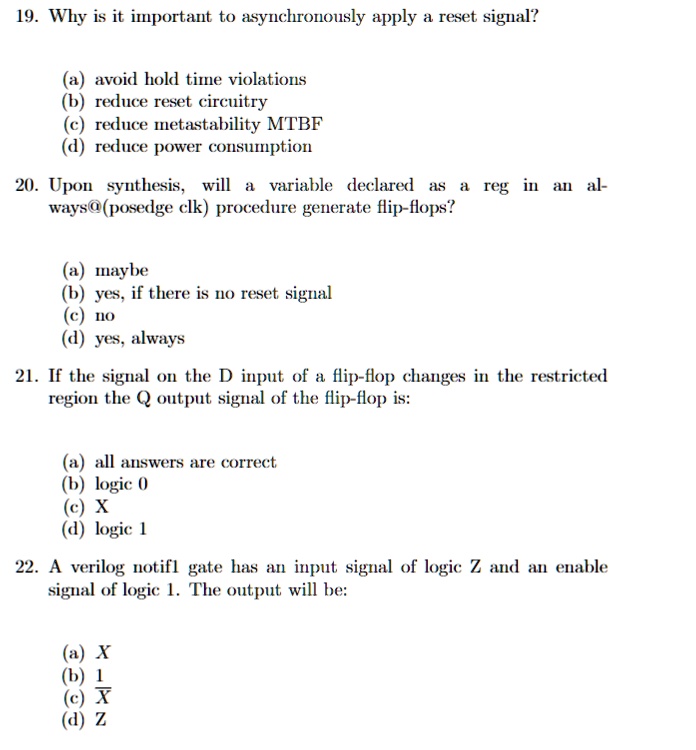

SOLVED: 19. Why is it important to asynchronously apply a reset signal? avoid hold time violations reduce reset circuitry reduce mnetastability MTBF reduce power COIISTption 20. Upon synthesis, will variable declared #5

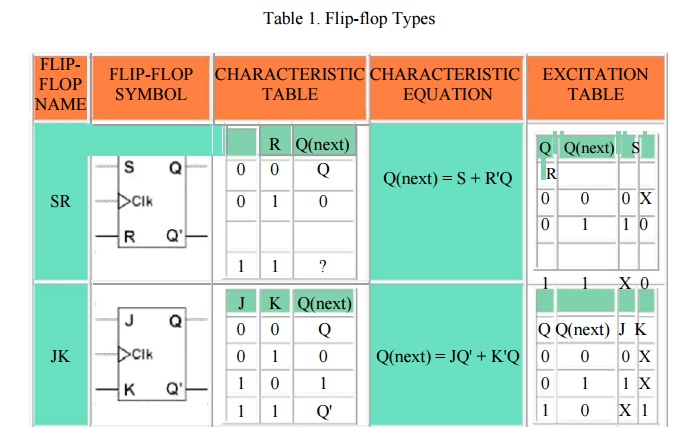

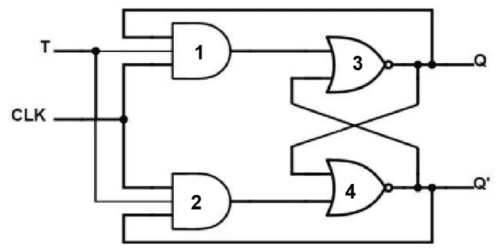

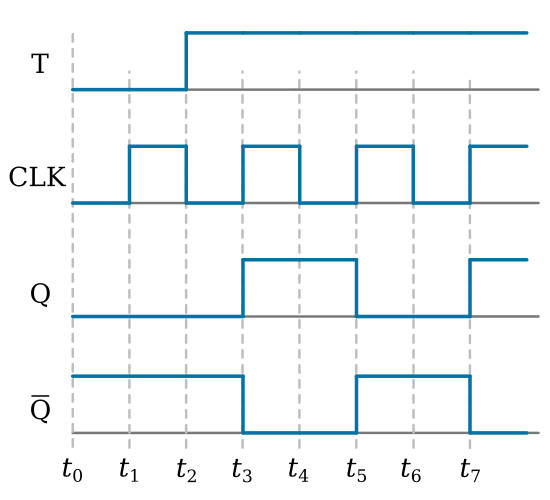

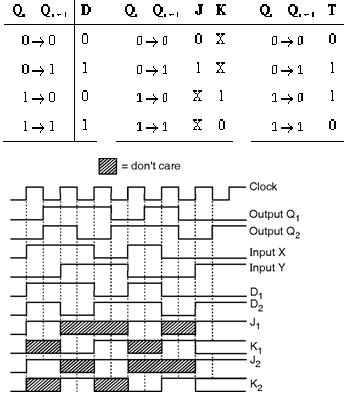

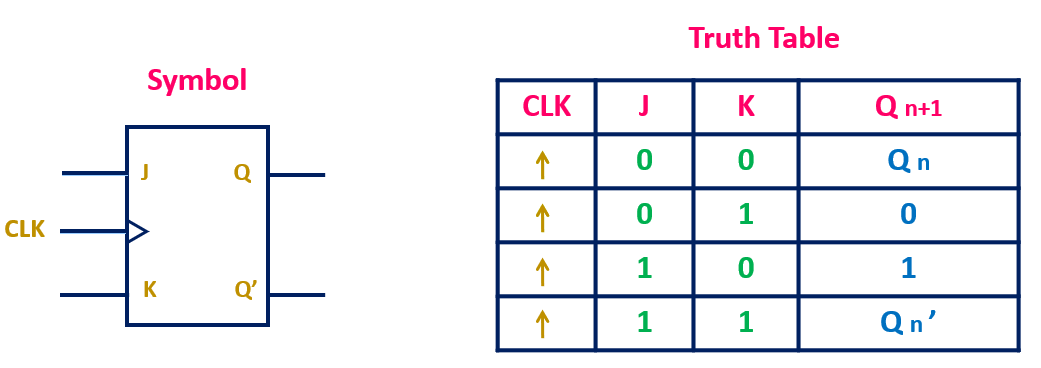

JK Flip-Flop Explained | Race Around Condition in JK Flip-Flop | JK Flip- Flop Truth Table, Excitation table and Timing Diagram - ALL ABOUT ELECTRONICS